# Xbridge ASIC Specification

Revision 0.5

for Rev A Si

Do not copy or distribute this document

Steven Miller

# Preface

This document specifies the functionality and operation of the Xbridge ASIC. In the course of developing this specification, many people provided valuable assistance. I would like to take this opportunity to thank them for the help that contributes to the creation of this specification.

XBridge is a combination of existing components (the Bridge and the Crossbow). I would like to thank the designers of the Bridge, Anan Nagarajan and the designers of the Crossbow, Rob Martin without whom this ASIC would not be possible.

I would like to thank John Keen for his review of this document.

4 11 3 34 V Ad.

| CHAPTER 1 | Overview                                                                                                                                                                                                                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1       | Part Name                                                                                                                                                                                                                                                                            |

| 1.2       | System Architecture Overview                                                                                                                                                                                                                                                         |

| 1.3       | Crossbow Subsection       18         1.3.1 Source Link       18         1.3.2 Destination Link       20         1.3.3 Widget 0       20         1.3.4 Crossbar Interconnect       20                                                                                                 |

| 1.4       | PCI Bridge Subsection                                                                                                                                                                                                                                                                |

|           | 1.4.1 Crosstalk Receive and Transmit Processors       22         1.4.2 PCI Bus (PCI Master & Slave)       23         1.4.3 Request Dispatcher       23         1.4.4 Request Generator and Prefetcher       23         1.4.5 Data Buffers       24         1.4.6 Interrupts       24 |

| 1.5       | Changes in Bridge                                                                                                                                                                                                                                                                    |

| 1.6       | Changes in Crossbow                                                                                                                                                                                                                                                                  |

| 1.7       | Related Documents                                                                                                                                                                                                                                                                    |

| 1.8       | Terms                                                                                                                                                                                                                                                                                |

| 1.9       | Signal Names                                                                                                                                                                                                                                                                         |

| 1.10      | Programmers Notes                                                                                                                                                                                                                                                                    |

| 1.11      | Reading This Document                                                                                                                                                                                                                                                                |

| CHAPTER 2 | Pin Descriptions31                                                                                                                                                                                                                                                                   |

| 2.1       | Pin Descriptions       31         2.1.1 Crosstalk Interface Pins       31         2.1.2 PCI Interface Pins       36         2.1.3 PCI PLL Pins       39         2.1.4 Miscellaneous Pins       40         2.1.5 Test Pins       41                                                   |

| CHAPTER 3 | XBridge Architecture                                                                                                                                                                                                                                                                 |

| 3.1       | Core Differences                                                                                                                                                                                                                                                                     |

| 3.2       | XBridge Mode                                                                                                                                                                                                                                                                         |

| 3.3       | Super Bridge Mode                                                                                                                                                                                                                                                                    |

| CHAPTER 4 | Crossbow Subsection Programmers Interface 47                                                                                                                                                                                                                                         |

| 4.1       | Overview                                                                                                                                                                                                                                                                             |

|           | Soft of the second                                                                            |            |

|-----------|-----------------------------------------------------------------------------------------------|------------|

|           | 4.1.2 Buffer Flush mechanism                                                                  | 55         |

|           | 4.1.3 Arbitration Control 4.1.4 Dual Host Support                                             | 55<br>57   |

| 4.:       |                                                                                               | 58         |

| 4.3       | Register Definitions                                                                          | 63         |

|           | 4.3.1 Link (x) Input Buffer Flush                                                             | 63         |

|           | 4.3.2 Link (x) Control Register                                                               | 63         |

|           | 4.3.3 Link (x) Status Register 4.3.4 Link (x) Auxiliary Status                                | 65         |

|           | 4.3.5 Link (x) Auxiliary Status  4.3.5 Link (x) Arbitration Upper                             | 67<br>68   |

|           | 4.3.6 Link (x) Arbitration Lower                                                              | 70         |

|           | 4.3.7 Link (x) Reset                                                                          | 70         |

|           | 4.3.8 Crossbow Identification                                                                 | 70         |

|           | 4.3.9 Crossbow Error Command Word 4.3.10 Crossbow Error Upper Address                         | 71         |

|           | 4.3.11 Crossbow Error Lower Address                                                           | 72<br>72   |

|           | 4.3.12 Crossbow Interrupt Destination Upper Address                                           | 73         |

|           | 4.3.13 Crossbow Interrupt Destination Lower Address                                           | 73         |

|           | 4.3.14 Crossbow Arbitration Reload                                                            | 74         |

|           | 4.3.15 Crossbow Packet Time-out register                                                      | 74         |

|           | 4.3.16 Crossbow Widget 0 Status 4.3.17 Crossbow Widget 0 Control                              | 74<br>76   |

|           | 4.3.18 Crossbow LLP Control                                                                   | 77         |

|           | 4.3.19 Crossbow Performance Counter A                                                         | 78         |

|           | 4.3.20 Crossbow Performance Counter B                                                         | 78         |

|           | 4.3.21 Crossbow NIC register 4.3.22 Crossbow Widget 0 Reset Fence                             | 78         |

|           | 4.3.23 Crossbow Widget o Reset Fence                                                          | 81<br>81   |

|           | 4.3.24 Crossbow Lock Register                                                                 | 82         |

| 4.4       | Function Errata                                                                               | 83         |

|           | 4.4.1 Double Overflow 4.4.2 Supported Crosstalk Packet Types                                  | 83<br>83   |

| CHAPTER 5 | Crossbar Subsection Architectural Description                                                 | .85        |

| 5.1       | Overview                                                                                      | 85         |

|           | 5.1.1 Clocking regimes                                                                        | 86         |

| 5.0       |                                                                                               |            |

| 5.2       |                                                                                               | 87         |

| 5.:       | 3 Link Controller                                                                             | 88         |

|           | 5.3.1 Source Link Controller 5.3.2 Source Sunghapana Receiver and Link Level Protect Passiver | 89         |

|           | 5.3.2 Source Synchronous Receiver and Link Level Protocol Receiver 5.3.3 Input Packet Buffer  | 90<br>93   |

|           | 5.3.4 Packet Receive Control                                                                  | 93         |

|           | 5.3.5 Free Buffer FIFO                                                                        | 94         |

|           | 5.3.6 Crossbar Request Manager                                                                | 95         |

|           | 5.3.7 Packet Dispatch Control 5.3.8 Exception module/Error handling                           | 100        |

|           | 5.3.9 Destination Link Controller                                                             | 102<br>108 |

|           | 5.3.10 Crossbar Connection Arbitration                                                        | 108        |

|           | 5.3.11 Free buffer issue logic and Crossbar Flow Control                                      | 112        |

|           | 5.3.12 Link Level Protocol Transmitter and Source Synchronous Driver                          | 113        |

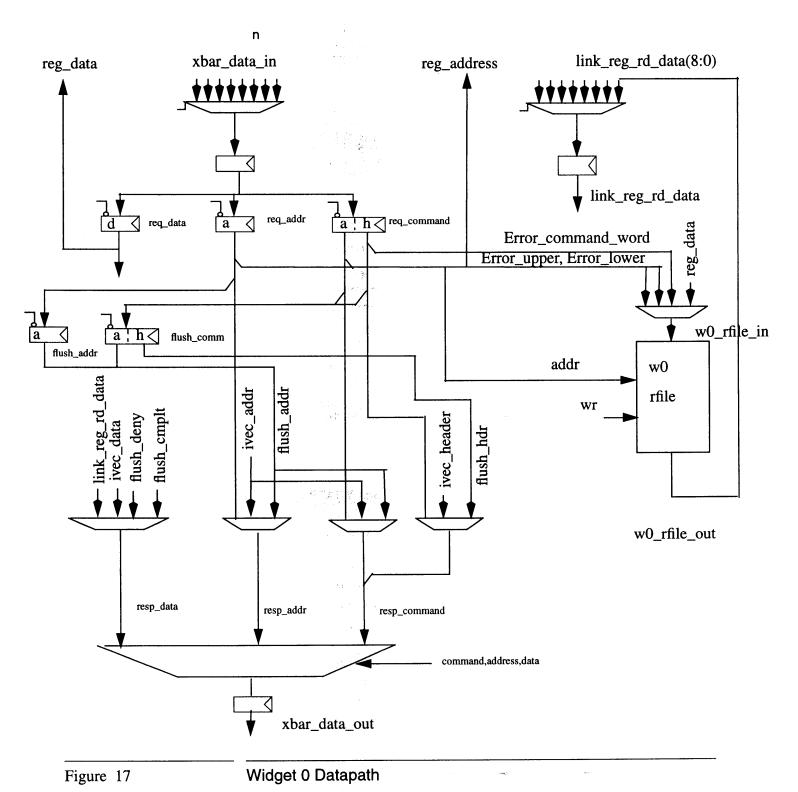

| 5.4       | Widget 0                                                                                      | 115        |

|           | 5.4.1 Internal Register Access                                                                | 116        |

|           |     | 5.4.2 Error Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 117                                                                              |

|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|           |     | 5.4.3 Interrupt processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 118                                                                              |

|           |     | 5.4.4 Buffer Flush Handling 5.4.5 Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 118<br>119                                                                       |

|           | 5.5 | Reset of Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 121                                                                              |

| CHAPTER 6 |     | PCI Bridge Internal Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23                                                                               |

|           | 6.1 | Internal Register Address Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 123                                                                              |

|           | 6.2 | Crosstalk Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 132                                                                              |

|           |     | 6.2.1 PCI Bridge Identification Register 6.2.2 PCI Bridge Status Register 6.2.3 PCI Bridge Error Upper Address 6.2.4 PCI Bridge Error Lower Address 6.2.5 PCI Bridge Control Register 6.2.6 PCI Bridge Request Time-out Value Register 6.2.7 PCI Bridge Interrupt Destination Upper Address Register 6.2.8 PCI Bridge Interrupt Destination Lower Address Register 6.2.9 PCI Bridge Error Command Word Register 6.2.10 PCI Bridge LLP Configuration Register 6.2.11 PCI Bridge Target Flush Register 6.2.12 Aux Error Command Word Register 6.2.13 Response Buffer Error Upper Address 6.2.14 Response Buffer Error Lower Address | 132<br>133<br>134<br>134<br>135<br>136<br>137<br>138<br>138<br>138<br>139<br>140 |

|           | 6.3 | 6.2.15 Test Pin Control Register  Mapping Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 140<br>142                                                                       |

|           | 0.0 | 6.3.1 PCI Bridge Direct Mapping Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 142                                                                              |

|           | 6.4 | Arbitration Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 142                                                                              |

|           | 6.5 | NIC Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 143                                                                              |

|           | 6.6 | PCI  6.6.1 Time-out Register  6.6.2 PCI Type 1 Configuration Register  6.6.3 PCI Error Upper Address Register  6.6.4 PCI Error Lower Address Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 144<br>144<br>145<br>145<br>146                                                  |

|           | 6.7 | Interrupt Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 146                                                                              |

|           |     | 6.7.1 INT_STATUS Register 6.7.2 INT_ENABLE Register 6.7.3 RESET_INT_STATUS Register 6.7.4 INT_MODE Register 6.7.5 INT_DEV Register 6.7.6 HOST_ERR_FIELD 6.7.7 Interrupt (x) Host Address Register 6.7.8 Error Interrupt View Register 6.7.9 Multiple Interrupt Register 6.7.10 Force Always Interrupt (x) Register 6.7.11 Force Interrupt (x) Register                                                                                                                                                                                                                                                                            | 147<br>150<br>151<br>152<br>153<br>154<br>154<br>155<br>157<br>159               |

|           | 6.8 | Device Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 159<br>161<br>163<br>163<br>165<br>166                                           |

|           |     | 6.8.6 Read Response Buffer Clear Register 6.8.7 PCI Bridge Buffer (x) Upper address Register 6.8.8 PCI Bridge Buffer (x) Lower Address Register                                                                                                                                                                                                                                                                                                                                | 166<br>167<br>168                             |

|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|           | 6.9 | Performance Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 168                                           |

|           |     | <ul> <li>6.9.1 Buffer (x) Flush Count with Data Touch Register</li> <li>6.9.2 Buffer (x) Flush Count w/o Data Touch Register</li> <li>6.9.3 Buffer (x) Request in Flight Count Register</li> <li>6.9.4 Buffer (x) Prefetch Request Count Register</li> <li>6.9.5 Buffer (x) Total PCI Retry Count Register</li> <li>6.9.6 Buffer (x) Max PCI Retry Count Register</li> <li>6.9.7 Buffer (x) Max Latency Count Register</li> <li>6.9.8 Buffer (x) Clear All Register</li> </ul> | 169<br>169<br>169<br>170<br>170<br>170<br>171 |

| CHAPTER 7 |     | PCI Bridge Address Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 173                                           |

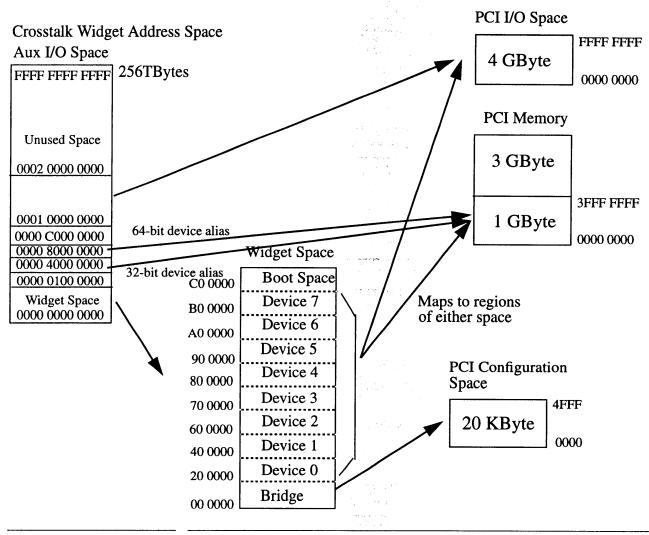

|           | 7.1 | Bus Address Maps                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 173<br>173<br>175                             |

|           | 7.2 | Crosstalk to PCI Bus Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 175                                           |

|           |     | <ul> <li>7.2.1 Crosstalk View of PCI</li> <li>7.2.2 Crosstalk Mapping Registers</li> <li>7.2.3 Crosstalk Widget Space Address Map</li> </ul>                                                                                                                                                                                                                                                                                                                                   | 175<br>177<br>179                             |

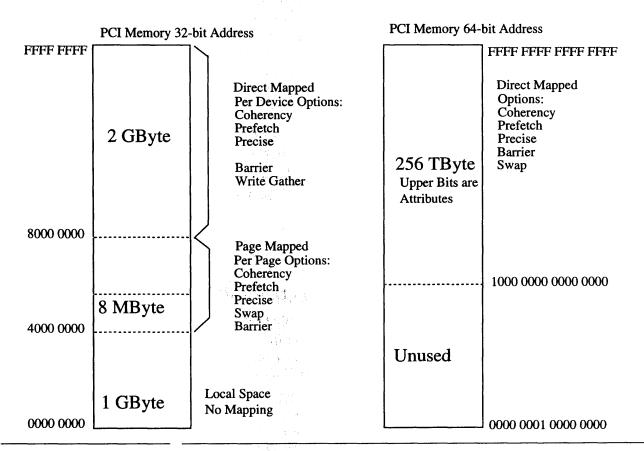

|           | 7.3 | PCI Bus to Crosstalk Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 180                                           |

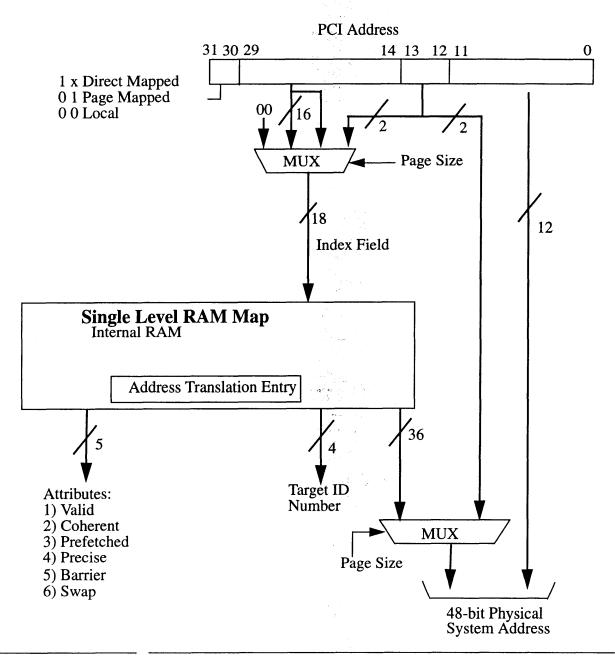

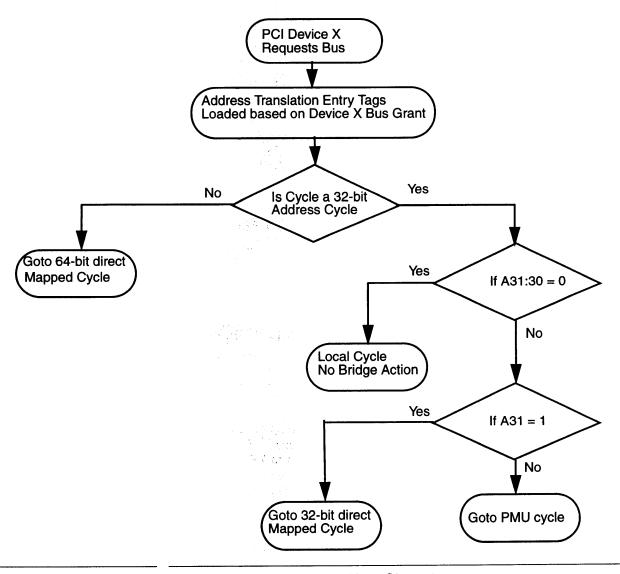

|           |     | <ul> <li>7.3.1 PCI View of Crosstalk</li> <li>7.3.2 PCI Direct Mapping</li> <li>7.3.3 PCI Page Mapping</li> <li>7.3.4 Packetization of PCI Operations</li> <li>7.3.5 PCI Address Translation Flow Chart</li> </ul>                                                                                                                                                                                                                                                             | 181<br>182<br>186<br>189<br>189               |

| CHAPTER 8 |     | PCI Interface Unit and It's Operation                                                                                                                                                                                                                                                                                                                                                                                                                                          | 193                                           |

|           | 8.1 | PCI Bus Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 193                                           |

|           |     | <ul> <li>8.1.1 PCI Commands</li> <li>8.1.2 PCI Basic Operations</li> <li>8.1.3 Termination</li> <li>8.1.4 PCI Arbitration</li> </ul>                                                                                                                                                                                                                                                                                                                                           | 194<br>195<br>197<br>198                      |

|           | 8.2 | Unsupported PCI Features                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 199                                           |

|           | 8.3 | Bridge PCI Operations  8.3.1 Crosstalk Writes PCI  8.3.2 Crosstalk Reads PCI  8.3.3 Interrupt Acknowledge  8.3.4 PCI Writes Crosstalk  8.3.5 PCI Reads Crosstalk                                                                                                                                                                                                                                                                                                               | 200<br>200<br>200<br>201<br>201<br>202        |

|           | 8.4 | Bridge PCI Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 203                                           |

|           | 8.5 | Bridge PCI Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 206                                           |

|           | 8.6 | PCI Configuration Space ID Select                                                                                                                                                                                                                                                                                                                                                                                                                                              | 206                                           |

| CHAPTER 9  |      | PCI Bridge Subsection Data Buffers                                           | . 209                      |

|------------|------|------------------------------------------------------------------------------|----------------------------|

|            | 9.1  | Data Buffer Overview                                                         | . 209                      |

|            | 9.2  | Widget Master Buffers                                                        | . 209                      |

|            | 9.3  | PCI Master Buffers  9.3.1 Read Response Buffers  9.3.2 Write Request Buffers | . 210<br>210<br>213        |

| CHAPTER 10 |      | PCI Interrupts                                                               | . 215                      |

|            | 10.1 | Bridge Interrupt Introduction                                                | . 215                      |

|            | 10.2 | Interrupt Operations                                                         | . 216                      |

| CHAPTER 11 |      | PCI Bridge Subsection Error Cases                                            | . 219                      |

|            | 11.1 | Incoming Crosstalk Packets                                                   | . 219<br>220<br>221<br>223 |

|            | 11.2 | Outgoing Crosstalk Packets                                                   | . 223                      |

|            | 11.3 | SSRAM Parity Errors                                                          | . 224                      |

|            | 11.4 | PCI Errors                                                                   | . 224<br>224<br>225        |

|            | A.1  | Big Endian System                                                            | . 228<br>228<br>232        |

|            | A.2  | Little Endian System                                                         | . 236<br>236<br>240        |

|            | B.1  | Rev1.0                                                                       | . 245                      |

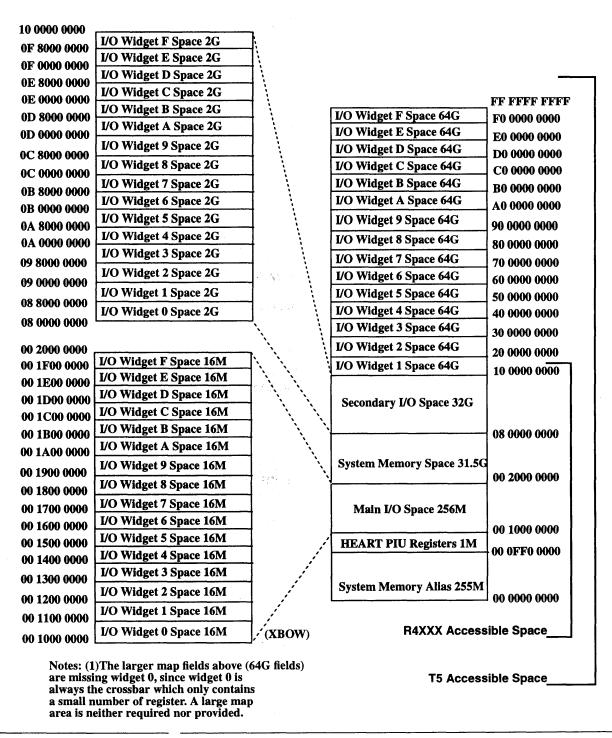

|            | C.1  | Addressing in a Godzilla System                                              | . 247                      |

|            | 11.5 | Current Anomalies in Rev1 Si                                                 | 254                        |

John Karley garier

| Figure        | 1  | XBridge System Block Diagram                    |

|---------------|----|-------------------------------------------------|

| Figure        | 2  | Super Bridge Mode Block Diagram                 |

| Figure        | 3  | XBridge Block Diagram18                         |

| Figure        | 4  | XBridge Bridge Subsection Block Diagram22       |

| Figure        | 5  | Crossbow Block Diagram86                        |

| Figure        | 6  | Crossbar Switch                                 |

| Figure        | 7  | Source Link Controller90                        |

| Figure        | 8  | 92                                              |

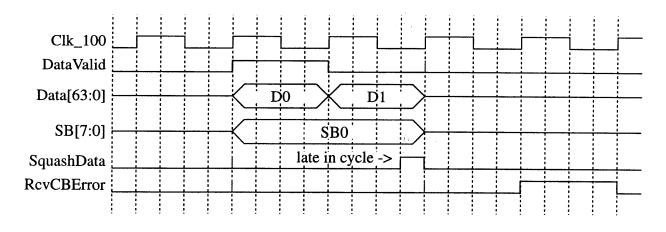

| Figure        | 9  | LLPr interface 16 bit mode, with packet error93 |

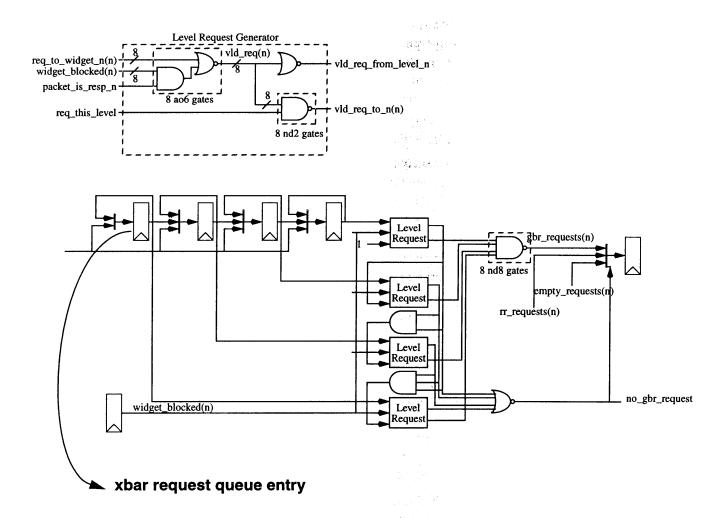

| Figure        | 10 | XBAR Request Dispatch96                         |

| Figure        | 11 | Request Manager Detail97                        |

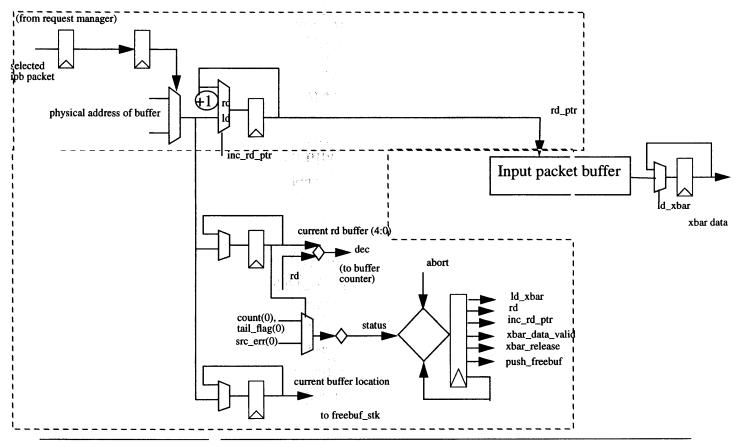

| Figure        | 12 | Packet Dispatch Control                         |

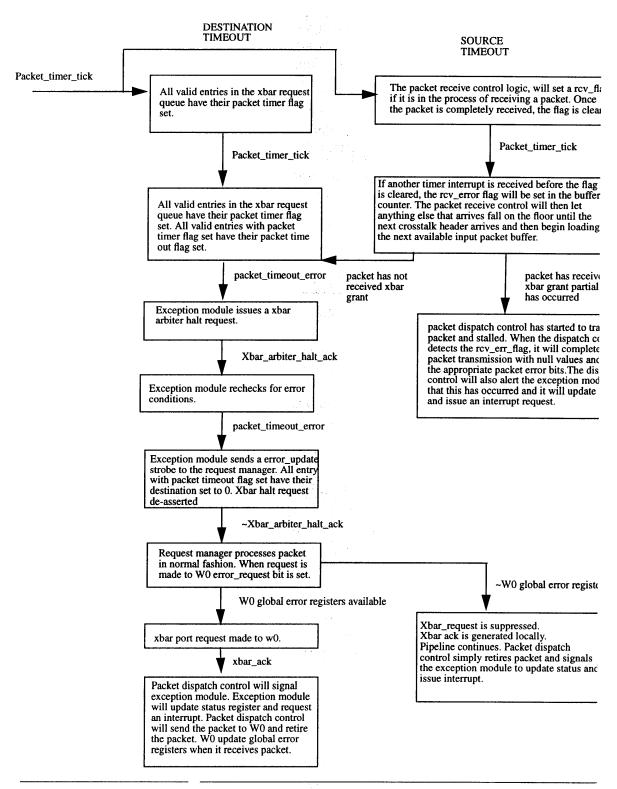

| Figure        | 13 | Flow diagram packet time-out processing         |

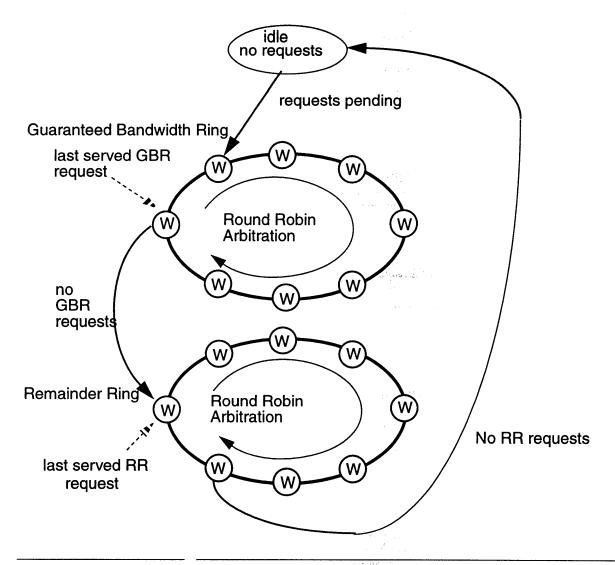

| Figure        | 14 | Crossbar Connection Arbitration Diagram111      |

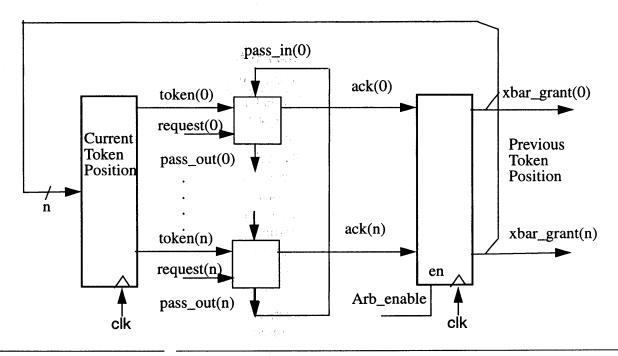

| Figure        | 15 | General Ring Arbitration Implementation         |

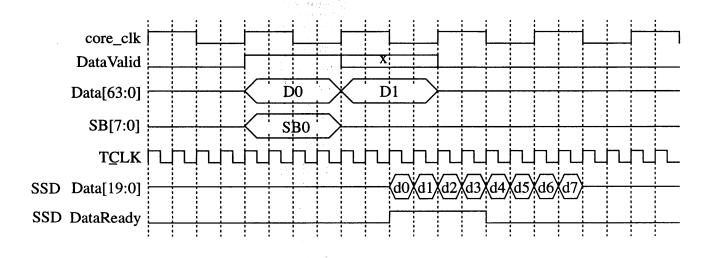

| Figure        | 16 | LLPt transmitting                               |

| Figure        | 17 | Widget 0 Datapath                               |

| Figure        | 18 | Crosstalk View of the PCI Bus                   |

| Figure        | 19 | 32-bit Address PCI View of Crosstalk            |

| Figure        | 20 | PCI PMU                                         |

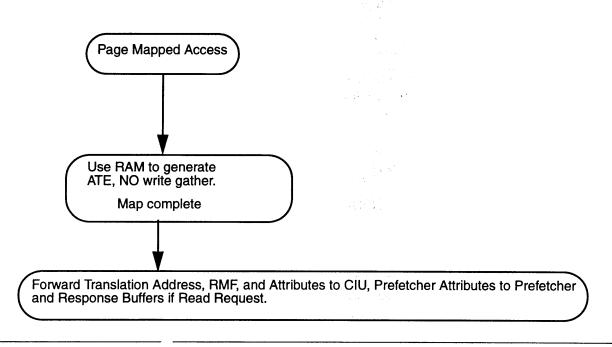

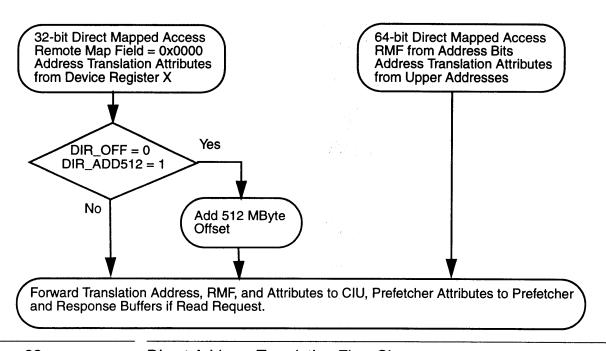

| Figure        | 21 | PCI Address Translation Flow Chart 1            |

| Figure        | 22 | PMU Address Translation Flow Chart              |

| Figure        | 23 | Direct Address Translation Flow Chart           |

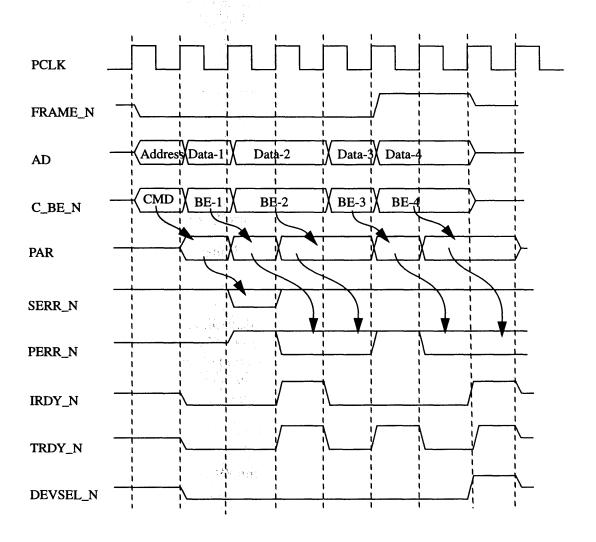

| Figure        | 24 | PCI Write (32-bit address)                      |

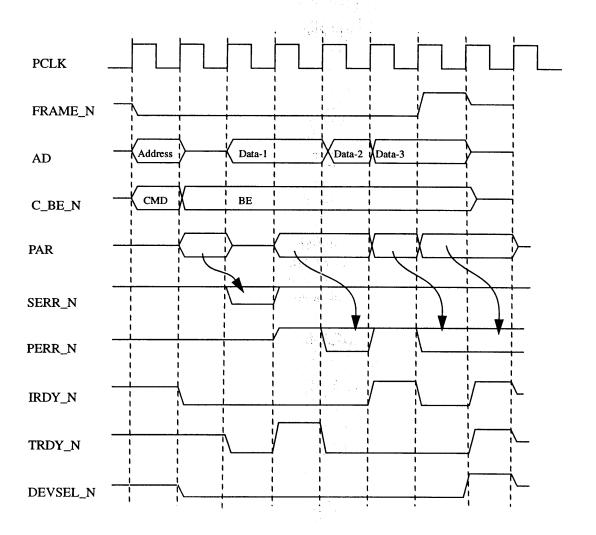

| <b>Figure</b> | 25 | PCI Read (32-bit address)197                    |

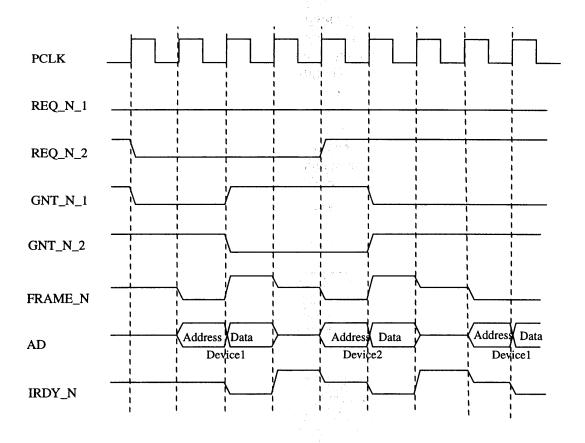

| Figure        | 26 | PCI Arbitration                                 |

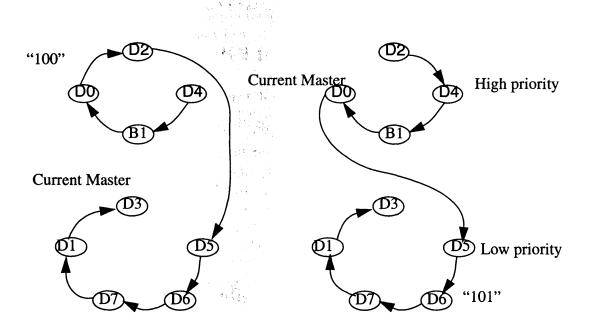

| Figure        | 27 | Arbitration Priority Rings                      |

| Figure        | 28 | Arbitration Examples                            |

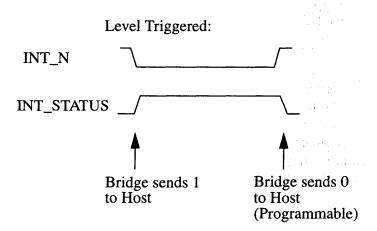

| Figure        | 29 | Level Triggered Interrupts                      |

| Figure        | 30 | Heart & R10000 Address Map to Bridge248         |

| Table | 1  | Port 8 Reset Fence Register                           | 27 |

|-------|----|-------------------------------------------------------|----|

| Table | 2  | Register Map Changes                                  | 28 |

| Table | 3  | Crosstalk Interface Pins                              | 31 |

| Table | 4  | PCI Bus Pins                                          | 36 |

| Table | 5  | PCI PLL Pins                                          | 39 |

| Table | 6  | Misc Pins                                             | 40 |

| Table | 7  | Test Pins                                             | 41 |

| Table | 8  | Link Controller Error Summary                         | 52 |

| Table | 9  | Widget 0 Error Conditions                             | 54 |

| Table | 10 | Widget 0 Register Address Map                         | 58 |

| Table | 11 | Link(x) Control Register                              | 63 |

| Table | 12 | Link(x) Status Register                               | 66 |

| Table | 13 | Link(x) Auxiliary Status                              | 67 |

| Table | 14 | Link (x) Arbitration Register                         | 69 |

| Table | 15 | Link (x) Arbitration Register                         | 70 |

| Table | 16 | Crossbow Identification Register                      | 71 |

| Table | 17 | Crossbow Error Command Word Register                  | 72 |

| Table | 18 | Crossbow Error Upper Address Register                 | 72 |

| Table | 19 | Crossbow Error Lower Address Register                 | 73 |

| Table | 20 | Crossbow Interrupt Destination Upper Address Register | 73 |

| Table | 21 | Crossbow Interrupt Destination Lower Address Register | 73 |

| Table | 22 | Crossbow Arbitration Reload Register                  | 74 |

| Table | 23 | Crossbow Packet Time-out register                     | 74 |

| Table | 24 | Crossbow Widget 0 Status Register                     | 75 |

| Table | 25 | Crossbow Widget 0 Control Register                    | 76 |

| Table | 26 | Crossbow LLP Control Register                         | 77 |

| Table | 27 | Crossbow Performance Counter A                        | 78 |

| Table | 28 | Crossbow Performance Counter B                        | 78 |

| Table | 29 | Crossbow NIC register                                 | 79 |

| Table | 30 | MicroLAN interface usage                              | 79 |

| Table | 31 | Number in a can contents                              | 80 |

| Table | 32 | Crossbow Widget 0 Reset Fence                         | 81 |

| Table | 33 | Crossbow Link 8 Reset Fence                           | 82 |

| Table | 35 | Supported Crosstalk Packet types                        | 83  |  |  |

|-------|----|---------------------------------------------------------|-----|--|--|

| Table | 36 | Xbar Request Queue Entry                                |     |  |  |

| Table | 37 | PCI Bridge Register Address Map                         |     |  |  |

| Table | 38 | PCI Bridge Identification Register                      | 132 |  |  |

| Table | 39 | PCI Bridge Status Register                              | 133 |  |  |

| Table | 40 | PCI Bridge Error Upper Address Register                 | 133 |  |  |

| Table | 41 | PCI Bridge Error Lower Address Register                 | 134 |  |  |

| Table | 42 | PCI Bridge Control Register                             | 134 |  |  |

| Table | 43 | PCI Bridge Request Time-out Value Register              | 135 |  |  |

| Table | 44 | PCI Bridge Interrupt Destination Upper Address Register | 136 |  |  |

| Table | 45 | PCI Bridge Interrupt Destination Lower Address Register | 136 |  |  |

| Table | 46 | PCI Bridge Error Command Word Register                  | 137 |  |  |

| Table | 47 | PCI Bridge LLP Configuration Register                   | 138 |  |  |

| Table | 48 | Aux Error Command Word Register                         | 138 |  |  |

| Table | 49 | Response Buffer Error Upper Address Register            | 139 |  |  |

| Table | 50 | Response Buffer Error Lower Address Register            | 140 |  |  |

| Table | 51 | Test Pin Control Register                               | 140 |  |  |

| Table | 52 | PCI Bridge Auxiliary Space and Direct Mapping Register  | 142 |  |  |

| Table | 53 | ARB_PRIORITY Register                                   | 142 |  |  |

| Table | 54 | NIC Register                                            | 143 |  |  |

| Table | 55 | PCI Time-out Register                                   | 144 |  |  |

| Table | 56 | PCI Type 1 Configuration Register                       | 145 |  |  |

| Table | 58 | PCI Error Lower Address Register                        | 146 |  |  |

| Table | 59 | Bridge INT_STATUS Register                              | 148 |  |  |

| Table | 60 | Bridge INT_ENABLE Register                              | 150 |  |  |

| Table | 61 | Bridge INT_RESET Register                               | 151 |  |  |

| Table | 62 | INT_MODE register                                       | 152 |  |  |

| Table | 63 | INT_DEV register                                        | 153 |  |  |

| Table | 64 | HOST_ERR_FIELD register                                 | 154 |  |  |

| Table | 65 | Interrupt (x) Host register                             | 154 |  |  |

| Table | 66 | Error Interrupt View Register                           | 155 |  |  |

| Table | 67 | Bridge INT_STATUS Register                              | 157 |  |  |

| Table | 68 | Device (x) Registers                                    | 161 |  |  |

| Table | 69        | Even Device Read Response Buffer Register                 | 163 |  |

|-------|-----------|-----------------------------------------------------------|-----|--|

| Table | 70        | Odd Device Read Response Buffer Register                  |     |  |

| Table | 71        | Read Response Buffer Status Register                      | 166 |  |

| Table | 72        | Read Response Buffer Clear Register                       | 166 |  |

| Table | 73        | PCI Bridge Buffer Upper Address Register                  | 167 |  |

| Table | 74        | PCI Bridge Buffer Lower Address Register                  | 168 |  |

| Table | <b>75</b> | Flush Count with Data Touch Register                      | 169 |  |

| Table | 76        | Flush Count without Data Touch Register                   | 169 |  |

| Table | <b>77</b> | In-flight Count Register                                  | 169 |  |

| Table | 78        | Prefetch Count Register                                   | 170 |  |

| Table | 79        | PCI Retry Count Register                                  | 170 |  |

| Table | 80        | Max PCI Retry Count Register                              | 170 |  |

| Table | 81        | Max Latency Count Register                                | 171 |  |

| Table | 82        | Bridge section of the XBridge PCI Memory Space Usage      | 174 |  |

| Table | 83        | Device Offset Index DEV_OFF                               | 178 |  |

| Table | 84        | Widget Space Address Map                                  | 179 |  |

| Table | 85        | PCI Configuration Space                                   | 180 |  |

| Table | 86        | 32-bit Direct Mapped Offset Address                       | 183 |  |

| Table | 87        | 64-bit Address Direct Map Attributes                      | 184 |  |

| Table | 88        | Direct Mapping Attributes Per Device                      | 184 |  |

| Table | 89        | Address Attributes In 32 Bit Address Direct Space         | 185 |  |

| Table | 90        | Address Attributes In 64 Bit Address Direct Space         | 186 |  |

| Table | 91        | Address Attributes In Page Mapped Space                   | 186 |  |

| Table | 93        | PCI Commands                                              | 194 |  |

| Table | 94        | Configuration ID Select Lines                             | 207 |  |

| Table | 95        | Response Packet Error Conditions                          | 220 |  |

| Table | 96        | Request Packet Error Conditions                           | 221 |  |

| Table | 97        | Receive Link Errors                                       | 223 |  |

| Table | 98        | Receive Link Errors                                       | 223 |  |

| Table | 99        | PCI Master Errors                                         | 224 |  |

| Table | 100       | PCI Slave Errors                                          | 225 |  |

| Table | 101       | Byte Data Big Endian SysAD to PCI-32 with Byte Swap       | 228 |  |

| Table | 102       | Half Word Data Big Endian SysAD to PCI-32 with Byte Swap. | 228 |  |

| Table | 103 | Word Data Big Endian SysAD to PCI-32 with Byte Swap 229      |        |  |

|-------|-----|--------------------------------------------------------------|--------|--|

| Table | 104 | Double Word Data Big Endian SysAD to PCI-32 with Byte Swap 2 |        |  |

| Table | 105 | Byte Data Big Endian SysAD to PCI-64 with Byte Swap 23       |        |  |

| Table | 106 | Half Word Data Big Endian SysAD to PCI-64 with Byte Swap.    | 231    |  |

| Table | 107 | Word Data Big Endian SysAD to PCI-64 with Byte Swap          | 231    |  |

| Table | 108 | Double Word Data Big Endian SysAD to PCI-64 with Byte Swap   | 232    |  |

| Table | 109 | Byte Data Big Endian SysAD to PCI-32 No Swap                 | 232    |  |

| Table | 110 | Half Word Data Big Endian SysAD to PCI-32 No Swap            | 233    |  |

| Table | 111 | Word Data Big Endian SysAD to PCI-32 No Swap                 | 233    |  |

| Table | 112 | Double Word Data Big Endian SysAD to PCI-32 No Swap          | 234    |  |

| Table | 113 | Byte Data Big Endian SysAD to PCI-64 No Swap                 | 234    |  |

| Table | 114 | Half Word Data Big Endian SysAD to PCI-64 No Swap            | 235    |  |

| Table | 115 | Word Data Big Endian SysAD to PCI-64 No Swap                 | 235    |  |

| Table | 116 | Double Word Data Big Endian SysAD to PCI-64 No Swap          | 236    |  |

| Table | 117 | Byte Data Little Endian SysAD to PCI-32 with Byte Swap       | 236    |  |

| Table | 118 | Half Word Data Little Endian SysAD to PCI-32 with Byte Swap  | 237    |  |

| Table | 119 | Word Data Little Endian SysAD to PCI-32 with Byte Swap       | 237    |  |

| Table | 120 | Double Word Data Little Endian SysAD to PCI-32 with Byte Swa | ip 238 |  |

| Table | 121 | Byte Data Little Endian SysAD to PCI-64 with Byte Swap       | 238    |  |

| Table | 122 | Half Word Data Little Endian SysAD to PCI-64 with Byte Swap  | 239    |  |

| Table | 123 | Word Data Little Endian SysAD to PCI-64 with Byte Swap       | 239    |  |

| Table | 124 | Double Word Data Little Endian SysAD to PCI-64 with Byte Swa | ip 240 |  |

| Table | 125 | Byte Data Little Endian SysAD to PCI-32 No Swap              | 240    |  |

| Table | 126 | Half Word Data Little Endian SysAD to PCI-32 No Swap         | 240    |  |

| Table | 127 | Word Data Little Endian SysAD to PCI-32 No Swap              | 241    |  |

| Table | 128 | Double Word Data Little Endian SysAD to PCI-32 No Swap       | 242    |  |

| Table | 129 | Byte Data Little Endian SysAD to PCI-64 No Swap              | 242    |  |

| Table | 130 | Half Word Data Little Endian SysAD to PCI-64 No Swap         | 243    |  |

| Table | 131 | Word Data Little Endian SysAD to PCI-64 No Swap              | 243    |  |

| Table | 132 | Double Word Data Little Endian SysAD to PCI-64 No Swap       | 244    |  |

| Table | 133 | Widget Base Address                                          | 249    |  |

| Table | 134 | Address Map From Base Address                                | 249    |  |

## CHAPTER 1 Overview

## 1.1 Part Name

Part Name: XBridge

SGI Part Number: 099-0182-001

Vendor: IBM

Vendor Part Number: 21L06674

Process Design Technology: SA-12 CMOS 5-Layer Metal

Package: 1088 CCGA 42mm w/ 87 mil columns

Die Size: 10.1mm x 10.1mm

Estimate Gate Count: 1,000 K

## 1.2 System Architecture Overview

The XBridge ASIC is a controller which provides an integration of the Crossbow and Bridge ASIC functionality. To that end, this document is the combination of the Crossbow and Bridge ASIC specifications. The

first sections are based on the Crossbow and the latter sections are the PCI Bridge.

33/66MHz PCI Busses (4-slot @ 33; 2-slots @ 66MHz)

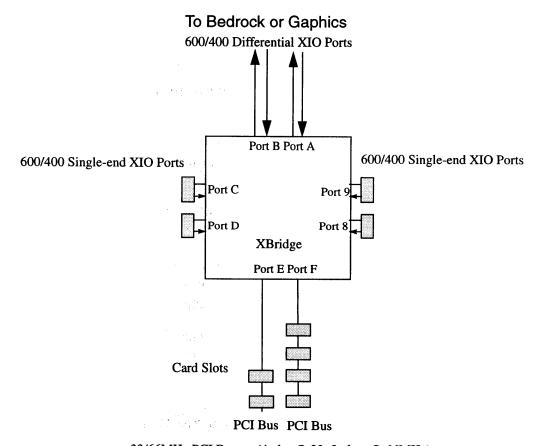

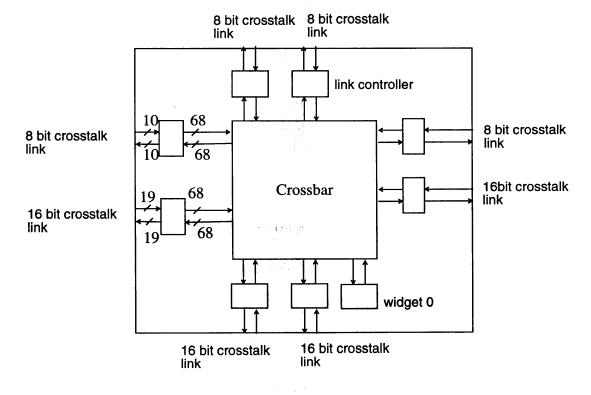

## Figure 1 XBridge System Block Diagram

The XBridge ASIC is a member of the Godzilla architecture family. Figure 1 contains a block diagram for a typical I/O system using XBridge. For a complete description of the Godzilla architecture please refer to the Godzilla Architecture Specification. The XBridge ASIC can be used to support I/O devices on either XIO or expansion with option card slots on the industry standard PCI bus.

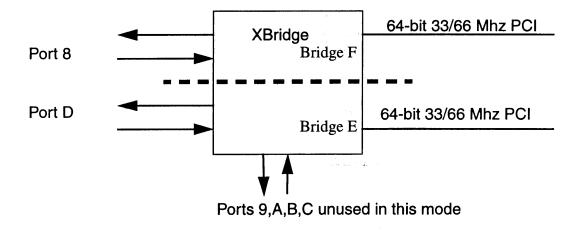

An XBridge can operate in two modes, the first (XBridge mode) is as shown in Figure 1, a combination of pci bridges and crossbow. The second mode, (Super Bridge mode) which allows the XBridge to function as

2 Bridge widgets each with a single pci bus. In this mode, four of the crosstalk ports and the internal crossbar are not used (See Figure 2). No communication between the pci busses is allowed internally. The basic operation of XBridge in this mode is like having two Bridge ASICs.

#### Figure 2

#### Super Bridge Mode Block Diagram

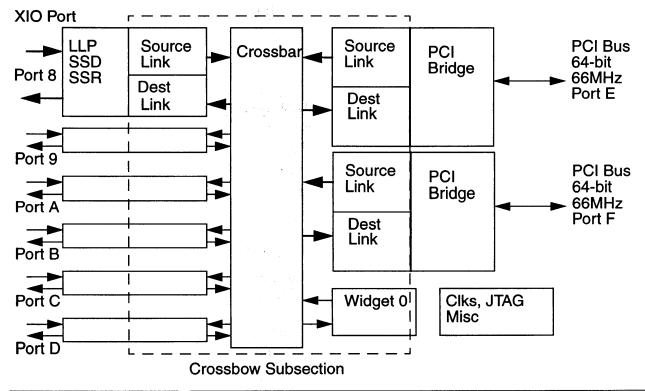

Shown in Figure 3 is a block diagram of the *XBridge* ASIC. The *XBridge* also contains a JTAG controller for boundary scan capability. The term XIO port is used in the systems environment to indicate a Crosstalk port. This document interchanges these terms throughout.

Figure 3 contains six major modules, the Source Link, the Destination Link, the Crossbar, Widget 0, which are all part of the Crossbow subsection. The Bridge subsection and the LLP.

Figure 3 XBridge Block Diagram

## 1.3 Crossbow Subsection

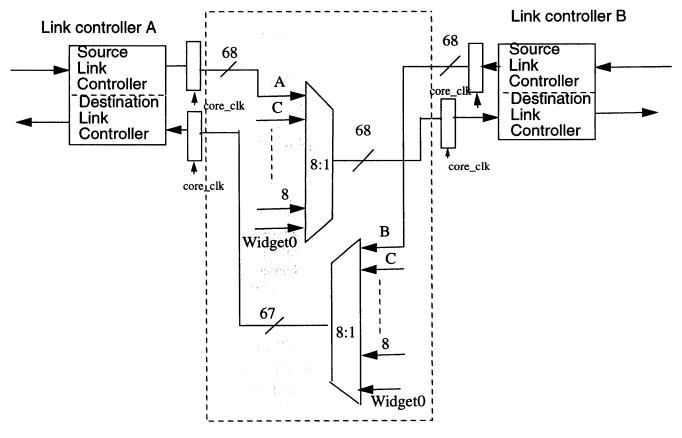

The Crossbar subsection consists of the Source Link, the Destination Link (Dest Link), the Crossbar, and Widget 0. Detailed operation and diagrams can be found in the Crossbow Subsection Architectural Description Chapter.

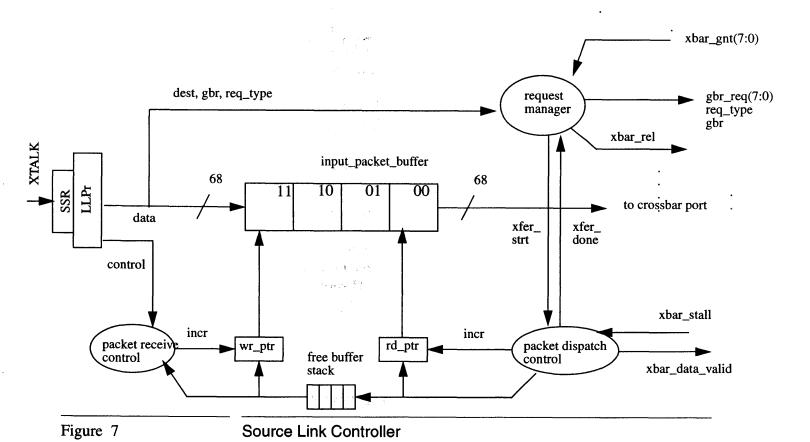

#### 1.3.1 Source Link

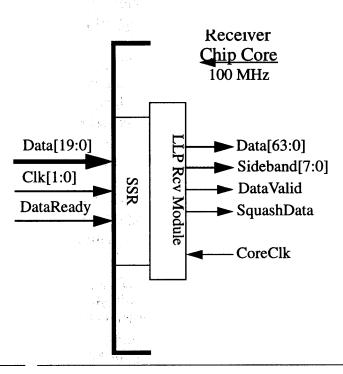

The source link controller (Source Link) handles all incoming traffic between the physical link interface (LLP) or PCI Bridge and the crossbar. The LLP handles the all Link Protocol and passes complete micropackets to the source link. The PCI Bridge also passes complete micropackets to the source link.

The source link's packet receive control logic scans the sideband data in the micropacket for "crosstalk packet start" code. If this is received the

control logic will begin filling one of 4 input packet buffers. The input packet buffer serves two purposes, it provides a place to park a crosstalk packet when the packet destination is busy and it provides for rate matching between the data stream coming from a LLP port operating in 8-bit mode and the crossbar. The Crossbow architecture is such that the crossbar transfers data at 800 Mbytes/sec; however, the LLP's provide data at either 400 Mbytes/sec or 800 Mbytes/sec depending on whether they are associated with 8 bit or 16 bit links respectively. The PCI Bridge always provides data at the 800 Mbytes/sec rate.

The packet receive logic will also write pertinent information from the command word portions of the packet and place it in the crossbar request queue which is located in the request manager section of the source link. The information written into the crossbar request queue defines the Crosstalk packet's destination, priority, and type (request or response). It is the request manager's job to determine which packets are eligible for arbitration and from among the packets that are eligible for arbitration select the packet which has the highest priority and arbitrate for a connection to that packet's destination crossbar port. While the crosstalk packet is being received and put into one of the input packet buffers, the request manager will check the status of the destination port (port\_status in the destination link) and the priority of the packets in the queue to determine which of the packets in the input packet buffer has the highest priority. Details of the request manager selection algorithm are left for the architectural description portions of this document.

If the packet which has just entered the queue has the highest priority of all packets currently in the queue, it will advance to the front of the queue and enter the crossbar connection arbitration phase. If there are higher priority crossbar connection requests already in the queue, it will wait until they are serviced.

During the crossbar arbitration phase the request manager sends a cross-bar connection request (port\_req) to the destination link controller (Dest Link) associated with the Crosstalk packet's destination. The request manager then alerts the packet dispatch control (in the Source Link) that a crossbar connection arbitration is in progress.

When the Crosstalk packet wins arbitration a port\_grant signal will be sent back from the destination link controller to the requesting source. The dispatch controller will begin transferring the packet out of the input packet buffer and into the crossbar. The request manager will then retire the entry from the request queue. As the dispatch controller is transferring the packet it monitors the destination's buffer full flag (Buffull). This

flag indicates to the source that the destination can currently accept no more data.

When the transfer of the packet nears completion the dispatch controller will release control of the destination port by asserting port\_release. This frees the crossbar connection arbiter to start a new arbitration phase and establish a new crossbar connection.

Once the dispatch controller has finished transferring the packet to the destination link, a "credit" is returned to the initiator widget. Credits are returned via the return sideband data stream. The credit indicates an input packet buffer slot has been freed.

#### 1.3.2 Destination Link

The central connection through which all link controllers pass data is the crossbar switch. The crossbar switch consists of 9 ports, 6 of which are used for external XIO ports, 2 for PCI interfaces, and the last for widget 0. Each crossbar connection consists of one 68 bit source port and one 68 bit destination port. The destination ports utilizes a 68 bit wide by 8 mux to establish a connection from the source ports. The 68 bits consist of 64 bits of data, 3 bits of sideband information and 1 bit of control (bit indicates valid data). The destination link controller's crossbar connection arbiter controls the mux. All data is registered in and registered out of the crossbar, hence it is a "one hop" interconnect.

#### **1.3.3** Widget 0

All access to internal registers in the crossbow is via widget 0. Widgets wishing to modify crossbow registers should direct their request packets to the widget 0 destination. Widget 0 behaves much the same as any set of link controllers. Source link controllers wishing to connect to widget 0 send a crossbar connection request to widget 0. The widget 0 crossbar connection arbiter will send an acknowledgment and then receive the packet. After widget 0 has received the packet it will perform the necessary operations on the Crossbow registers. If a response is required, widget 0 will then form a response packet and transfer it back to the initiating widget via the crossbar.

#### 1.3.4 Crossbar Interconnect

The central connection through which all link controllers pass data is the crossbar switch. The destination link controller's crossbar connection ar-

biter controls the mux. All data is registered in and registered out of the crossbar, hence it is a "one hop" interconnect.

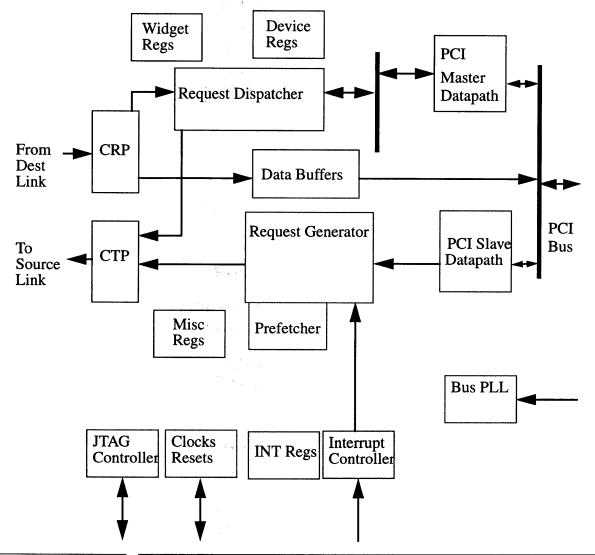

## 1.4 PCI Bridge Subsection

The figure below contains a block diagram of the PCI bridge sub section in the XBridge ASIC. The major subsections are the Crosstalk Transmit and Receive Processors (CTP & CRP), the Request Dispatcher, the PCI Master and Slave, the Interrupt Controller, the Data Buffers and the Request Generator /Prefetcher.

Figure 4 XBridge Bridge Subsection Block Diagram

#### 1.4.1 Crosstalk Receive and Transmit Processors

The PCI Bridge subsection communicates to the XBridge core through the *Crosstalk* Receive Processor (CRP) and *Crosstalk* Transmit Processor (CTP) CTP blocks. The *Crosstalk* receive and transmit processors provide link control and buffering of packets sent and received from the Crossbar (XBridge mode) or XIO port (Super Bridge mode). The Crosstalk Receive Processor (CRP) receives packets and transfers them

to either the data buffers (response packets) or the request dispatcher (request packets). The Crosstalk Transmit Processor (CTP) gathers responses and bus-generated requests and transmits them to other widgets.

### 1.4.2 PCI Bus (PCI Master & Slave)

The PCI Local Bus is a 32-bit or 64-bit bus with multiplexed address and data lines. The synchronous bus can operate at a speed up to 66 MHz in burst mode which provides a very high host/memory to peripheral transfer rate. For more detailed information please refer to the PCI Local Bus Specification revision 2.1. The bus is processor independent in that there are no processor specific operations which might exclude general purpose processors. Devices are configurable by the host. PCI devices can act as a bus master to transfer data to and from the host or they can access other local PCI devices or devices via the Crosstalk Interconnect. Supporting PCI Bus allows SGI to have a large number of third party high performance, low cost peripheral devices to choose from to provide most functionality and best I/O throughput while the I/O bus (PCI) can last for several generations without a need to change. The XBridge supports eight PCI devices. (Due to PCI loading restrictions, the XBridge can support only four add-in cards, loading will be less when operating at 66MHz.)

## 1.4.3 Request Dispatcher

The request dispatcher decodes and distributes all incoming requests to the different functional units. It is also responsible for returning the response from those requests, providing any address translation, and error checking. The *Crosstalk* to PCI bus translation mechanism consists of generating a PCI bus address from the *Crosstalk* address. This translation occurs using fixed regions defined in widget slot space and auxiliary I/O space. For detailed description of the address maps and use please refer to the PCI Bridge Address Mapping Chapter.

## 1.4.4 Request Generator and Prefetcher

The request generator is responsible for crosstalk request packet generation, address translation, and response buffer management. The request generator translation mechanism uses two mapping techniques, a direct map scheme for a portion of system memory and a page mapped scheme for the rest. The direct map scheme uses internal registers and predefined areas to perform mapping. The page map scheme uses a Page Mapping Unit (PMU) to perform address translation on a page basis.

To speed up the read access performed by the PCI devices to data residing across the *Crosstalk* Interconnect, the Prefetcher circuit will uses attributes from the address to decide whether to prefetch more data following current address. This enables faster read response time when sequential reads are performed by the PCI I/O devices.

#### 1.4.5 Data Buffers

Data Buffers provide data buffering between *Crosstalk* Interconnect and PCI circuit. It off loads read/write packets from high speed, non-stallable *Crosstalk* Bus to the lower performance, two-way handshaking PCI buses.

#### 1.4.6 Interrupts

Eight external active low interrupt pins from each PCI Bus are connected to the XBridge. The assignment of the pins is not predefined. All interrupt drivers should be open drain or open collector so that multiple devices can drive the same XBridge pin or one device can have multiple interrupt pins to report different cases. Any time there is a change on an interrupt pin, XBridge reports that to the host via a double word write packet. (Reporting the low to high transition of the active low pins can be individually disabled.) Each PCI subsection in XBridge will also send interrupts to the host when some abnormal conditions occur on the Crosstalk Bus or PCI Bus. These condition can be found in the PCI Bridge Subsection Error Cases Chapter.

Each interrupt condition is individually enabled or disabled by the host. The XBridge reports all the interrupt activities to the host while they are enabled. The XBridge does not maintain local interrupt priority and no interrupt condition can prevent the reporting of other interrupts.

## 1.5 Changes in Bridge

- 1) Remove GIO mode

- 2) Remove External SSRAM, reflect 0xc0\_0000 thru 0xff\_ffff on pci bus address 0x0 to 0x3f\_ffff.

- 3) Support 66MHz PCI operation

#### 4) fix the following:

Symptom: Arriving requests which do not contain the correct number of micro-packets as defined in the command word this will cause the request dispatcher to get out of sync. The request dispatcher detects the error and issues an interrupt but a read of the interrupt status register might not be possible due to the error.

Symptom: The bridge does not assert REQ64\* during reset to indicate that the bridge is capable of 64-bit data transfers.

Symptom: Control or LLP register writes can cause a hang if followed by any other internal operation other than a read of the register which was written.

5) Error Interrupts: allow disabled error conditions to be observable in some register.

error view register 0x170 error multiple register 0x178

- 6) Provide a single NIC pin operated from Widget 0 in XBridge mode, and from Bridge at Port F in Super Bridge Mode.

- 7) Credit count: make the count readable through a register.

bits 15:8 in status register for tx and tx credit counts

- 8) Increase the size of the internal page map to either 512 entries and also removing the RMF field from page map (RMF always 0).

- 9) Add a swap per ATE entry.

- 10) Clock out 66 and 33 only, no enables.

- 11) Add view to read response buffer addresses

buffer 0 low 0x300

buffer 0 hi 0x308

. . . . . . . . . .

buffer 15 low 0x3f0

buffer 15 hi 0x3f8

12) Remove the following registers ssram parity error 0x90

- 13) remove pending and max trans fields from control register.

- 14) Add 8 misc inputs for each bridge viewable through bridge status reg bits 7:0

- 15) Add 4 more outputs to test outputs on each bridge.

- 16) Add swap attribute in 64-bit PCI slave mode.

- 17) remap the rest of pci mapped space to direct space.

- 18) Add Interrupt generation via PIO in two modes: first, PIO always generates interrupt; second, interrupt pin active and PIO required to generate interrupt.

#### Will not Fix:

- 1) Symptom: If a prefetch read stream is flushed by an interrupt while the stream is currently active and the interrupt pin is held low for multiple pci clocks, the re-request of the flushed op can be sent multiple times. This is caused by the pci fsm issuing the operation and the interrupt controller marking the op flushed. This has a tiny performance penalty in that the op is fetched twice if it occurs.

- 2) Symptom: PIOs cause any partial write buffer, for device 0 only, to prematurely flush. There is no correctness issues just a were slight performance penalty.

## 1.6 Changes in Crossbow

1.) Source ID field added to the widget 0 status register. Bits 9:6 of the Crossbow Widget 0 Status register now contain a field which indicates the port that the read request originated from. So a widget may determine which port it is connected to by simply reading the widget 0 status register.

#### 2.) Warm Reset Fences added:

Nine 8 bit registers have been added to widget 0. Each register is associated with a xbow port or widget 0. The bits in each register determine which source ports are the port will accept warm resets. These registers are reset only by power on reset.

| Field               | Bits | Reset * | Access | Description                                                                                                                          |

|---------------------|------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| Reserved            | 31:8 |         |        |                                                                                                                                      |

| WarmReset from F Ok | 7    | 1       | R/W    | 0:Warm resets are blocked if they originate from this block. 1:Warm reset from this block will cause Port 8 to receive a warm reset. |

| WarmReset from E Ok | 6    | 1       | R/W    |                                                                                                                                      |

| WarmReset from D Ok | 5    | 1       | R/W    |                                                                                                                                      |

| WarmReset from C Ok | 4    | 1, 1,   | R/W    |                                                                                                                                      |

| WarmReset from B Ok | 3    | 1       | R/W    |                                                                                                                                      |

| WarmReset from A Ok | 2    | 1       | R/W    |                                                                                                                                      |

| WarmReset from 9 Ok | 1    | 1       | R/W    |                                                                                                                                      |

| WarmReset from 8 Ok | 0    | 1       | R/W    |                                                                                                                                      |

Table 1

Port 8 Reset Fence Register

| Register                                 | Address        |

|------------------------------------------|----------------|

| XBow widget0 reset fence                 | 0x00_0000_0078 |

| XBow Link 8 reset fence                  | 0x00_0000_0080 |

| XBow Link 9 reset fence                  | 0x00_0000_0088 |

| XBow Link A reset fence                  | 0x00_0000_0090 |

| XBow Link B reset fence                  | 0x00_0000_0098 |

| XBow Link C reset fence                  | 0x00_0000_00A0 |

| XBow Link D reset fence                  | 0x00_0000_00A8 |

| XBow Link E reset fence                  | 0x00_0000_00B0 |

| XBow Link F reset fence                  | 0x00_0000_00B8 |

| en e |                |

#### Table 2

#### **Register Map Changes**

#### 3.) General Purpose Lock register added:

An 8 bit register was added as a general lock register. Presumably it will be used to determine who owns the NIC/microlan resource. Upon power on reset the register is cleared to all zeroes. A write to location  $0x00\_0000\_00C0$  will occur only if the current value is all zeroes. A write to location  $0x00\_0000\_C8$  will clear the register. The register may be read from either location. It is presumed that on power up a host widget will read its source id from the widget0 status register, write this value into the lock register, and then read to see if it obtain the lock. If would then release the lock by writing the lock registers clear address.

#### 4.) Watchdog timers added to Widget0:

Originally widget 0 was not designed to recovered from a crashed host. It was assumed that if the host widget was not responding eventually a reset would be coming. In a dual host situation, a widget 0 that is hung waiting for a destination to respond or a source to release a connection would be a bad thing indeed. If a source does not release the widget 0 port after 8 time-out intervals as set per the Crossbow Packet Time-out register, the arbiter will time-out, set bit 3 in the widget 0 status register to indicate a source time-out occurred. Widget 0 will then complete the transaction

and grant the next requestor access to the widget 0 port. Similarly, if a destination port never grants access to a widget 0 request, bit 1 in the widget 0 status register will be set to indicate a destination time-out error occurred and the transaction will complete. This feature is not enabled unless explicitly enabled by setting bit 4 in the widget 0 control register.

#### 1.7 Related Documents

- Crosstalk Interconnect Specification, Revision 1.4, by Steven Miller, and James Tornes

- Bridge ASIC Specification, Revision 3.0,

by Steve Miller and Ching Hu

- PCI Local Bus Specification, Revision 2.1

- Link Level Protocol Specification by Mike Galles

- Godzilla Architecture Specification

by Karim Abdalla, Steven Miller, James

- by Karim Abdalla, Steven Miller, James Tornes, Ross Werner, and Daniel Yau

- by Rick Jeng, Karim Abdalla, Daniel Yau, and James Tornes

**HEART** Specification

- Crossbow Specification, Revision 13.0

by Pravin Shah, Rob Martin

- Speed Racer Product Specification, Revision 2.0 by Ross Werner

## 1.8 Terms

It is assumed the reader has read the Crosstalk Interconnect specification and has thorough knowledge of the Crosstalk Interconnect protocol, packet formats, and electrical characteristics. The following terms are discussed in the Crosstalk Interconnect specification and used throughout this document:

WIDGET Any ASIC connected to the Crossbar ASIC with

Crosstalk interconnect links.

**TARGET** The destination widget of a Crosstalk packet.

INITIATOR

The source widget of a packet.

**LINK**

The physical connection from the Bridge ASIC to any

Crossbar.

#### CROSSTALK PACKET

The minimum unit of data transfer on the Crosstalk Interconnect. Data transfer on the Crosstalk Interconnect occurs only in several fixed data packet sizes ranging from a double word value (8 bytes), to a full cache line (128 bytes), plus header.

**CROSSBAR**

Central routing agent for packets. Examples are

Crossbow and XBridge.

## 1.9 Signal Names

Signal names that end in \_N denote signals that are active low. The term "assert" means to drive to an active state, "de-assert" means to drive to an inactive state. Buses are denoted by **BUSNAME(MSB:LSB)**.

## 1.10 Programmers Notes

Throughout the text in the following sections are programmers notes shown in italics to call attention to specific functions or frequently asked questions.

## 1.11 Reading This Document

This document like the XBridge itself is a merge of the Crossbow and Bridge ASICs. Every attempt has been made to update the Crossbow and Bridge sections to reflect any changes. Where conflicts exists, please refer to the Register and XBridge Architecture Sections for resolution.

# CHAPTER 2 Pin Descriptions

## 2.1 Pin Descriptions

For more detailed information on Crosstalk Signals please refer to the Crosstalk Interconnect Specification, and PCI Signals please refer to the PCI Local Bus Specification. In addition to signal name and description, the direction and buffer type is listed in the pin table. Xbridge has 3 types of I/O pins, 3.3V compliant, 2.5V compliant and STL. For more information on STL please refer to the Crosstalk Designer's Guide. The term "Crossbar Generated" signals is a generic term used to indicate signals generated by a ASIC which operates as a Crossbar. For the 6 Crosstalk Ports, XBridge operates as a Crossbar in XBridge mode.

#### 2.1.1 Crosstalk Interface Pins

Xbridge supports 6 Crosstalk ports indexed 8 through D. The first 2 characters (X8, X9) indicate which port.

| Names                    | I/O | Types    | Description                                                                             |

|--------------------------|-----|----------|-----------------------------------------------------------------------------------------|

| P8_O_CLK_H<br>P8_O_CLK_L | 0   | Diff STL | Crossbar Generated Clock used when packets are transferred from the crossbar to widget. |

Table 3

| Names                    | I/O | Types     | Description                                                                                        |

|--------------------------|-----|-----------|----------------------------------------------------------------------------------------------------|

| P8_O_CD(19:0)            | О   | STL       | Crossbar Crosstalk Data <19:0> Micro packet data from crossbar to widget. {synchronous to O_CLK}   |

| P8_O_DRDY_L              | О   | STL       | Crossbar Data Ready indicating the start valid micro packet on link. {synchronous to O_CLK}        |

| P8_I_CLK_H<br>P8_I_CLK_L | I   | Diff STL  | Widget Generated Clock used when packets are transferred from the widget to the crossbar.          |

| P8_I_CD(19:0)            | I   | STL       | Widget Crosstalk Data <19:0> Micro packet data from Bridge to the crossbar. {synchronous to I_CLK} |

| P8_I_DRDY_L              | I   | STL       | Widget Data Ready indicating the start valid micro packet on link. {synchronous to I_CLK}          |

| P8_VREF(1,2)             | I   | STL       | Crosstalk STL Voltage Reference                                                                    |

| P8_LINK ALIVE            | О   | 2.5V CMOS | Crosstalk Link Alive indicates that the link has completed reset negotiation correctly.            |

| P8_W_PRESENT_N           | I   | 2.5V CMOS | Crosstalk Widget Present                                                                           |

| P8_W_SPEED               | I   | 2.5V CMOS | Crosstalk Widget XIO Speed 1= 600 0=400                                                            |

| P9_O_CLK_H<br>P9_O_CLK_L | 0   | Diff STL  | Crossbar Generated Clock used when packets are transferred from the crossbar to widget.            |

| P9_O_CD(19:0)            | О   | STL       | Crossbar Crosstalk Data <19:0> Micro packet data from crossbar to widget. {synchronous to O_CLK}   |

| P9_O_DRDY_L              | 0   | STL       | Crossbar Data Ready indicating the start valid micro packet on link. {synchronous to O_CLK}        |